Visual Odometry Part Deux

Created on 27 Nov 2015

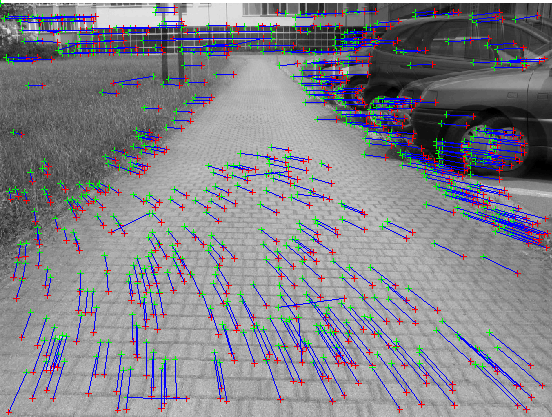

Visual Odometry Coprocessor on an Altera FPGA

For my digital design capstone (18-545), I worked a stereoscopic visual odometry coprocessor on a Xilinx FPGA (Zedboard). However, the Xilinx tools are very poorly documented and quite difficult to use.

Altera has a similar FPGA to the Zedboard, so I wanted to see how much easier (or more difficult) the Altera tools are to use. The goal of the project will be to port the original project to the DE-1 SoC board (Cyclone V family).

@bmperez

Brandon Perez

| Part | Cost | Quantity | Total |

| Terasic - SoC Platform - Cyclone - DE1-SoC Board | $249.00 | 1 | $249.00 |

| The FPGA system I will be using to create the system. It is $175 if you use the Academic discount. | |||

| Project Totals: | 1 | $249.00 | |

| Track 1 Base Budget: | $250.00 | ||

| Preferred Vendor Budget Bonus: | $0.00 | ||

| Remaining Budget: | $1.00 | ||